Xuantie-C920R2S1-User-Manual

Jun 07, 2024

#### Copyright © 2023 Hangzhou C-SKY MicroSystems Co., Ltd. All rights reserved.

This document is the property of Hangzhou C-SKY MicroSystems Co., Ltd. and its affiliates ("C-SKY"). This document may only be distributed to: (i) a C-SKY party having a legitimate business need for the information contained herein, or (ii) a non-C-SKY party having a legitimate business need for the information contained herein. No license, expressed or implied, under any patent, copyright or trade secret right is granted or implied by the conveyance of this document. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise without the prior written permission of Hangzhou C-SKY MicroSystems Co., Ltd.

#### Trademarks and Permissions

The C-SKY Logo and all other trademarks indicated as such herein (including XuanTie) are trademarks of Hangzhou C-SKY MicroSystems Co., Ltd. All other products or service names are the property of their respective owners.

#### Notice

The purchased products, services and features are stipulated by the contract made between C-SKY and the customer. All or part of the products, services and features described in this document may not be within the purchase scope or the usage scope. Unless otherwise specified in the contract, all statements, information, and recommendations in this document are provided "AS IS" without warranties, guarantees or representations of any kind, either express or implied.

The information in this document is subject to change without notice. Every effort has been made in the preparation of this document to ensure accuracy of the contents, but all statements, information, and recommendations in this document do not constitute a warranty of any kind, express or implied.

#### 杭州中天微系统有限公司 Hangzhou C-SKY MicroSystems Co., LTD

Address: Room 201, 2/F, Building 5, No.699 Wangshang Road , Hangzhou, Zhejiang, China

Website: www.xrvm.cn

### Copyright © 2023 杭州中天微系统有限公司, 保留所有权利.

本文档的所有权及知识产权归属于杭州中天微系统有限公司及其关联公司(下称"中天微")。本文档仅能分派给:(i)拥有合法雇佣关系,并需要本文档的信息的中天微员工,或(ii)非中天微组织但拥有合法合作关系,并且其需要本文档的信息的合作方。对于本文档,未经杭州中天微系统有限公司明示同意,则不能使用该文档。在未经中天微的书面许可的情形下,不得复制本文档的任何部分,传播、转录、储存在检索系统中或翻译成任何语言或计算机语言。

### 商标申明

中天微的 LOGO 和其它所有商标(如 XuanTie 玄铁)归杭州中天微系统有限公司及其关联公司所有,未经杭州中天微系统有限公司的书面同意,任何法律实体不得使用中天微的商标或者商业标识。

#### 注意

您购买的产品、服务或特性等应受中天微商业合同和条款的约束,本文档中描述的全部或部分产品、服务或特性可能不在您的购买或使用范围之内。除非合同另有约定,中天微对本文档内容不做任何明示或默示的声明或保证。

由于产品版本升级或其他原因,本文档内容会不定期进行更新。除非另有约定,本文档仅作为使用指导,本文档中的所有陈述、信息和建议不构成任何明示或暗示的担保。杭州中天微系统有限公司不对任何第三方使用本文档产生的损失承担任何法律责任。

### 杭州中天微系统有限公司 Hangzhou C-SKY MicroSystems Co., LTD

地址: 中国浙江省杭州市网商路 699 号 5 号楼 2 楼 201 室

网址: www.xrvm.cn

# Version History

| Version | Description                                                            | Date       |

|---------|------------------------------------------------------------------------|------------|

| 01      | Initial release.                                                       | 2021.07.31 |

| 02      | Added simplified power-off scenarios. Updated vector descriptions.     | 2021.09.17 |

| 03      | Updated address encoding description of pmpaddr.                       | 2021.10.25 |

| 04      | Various updates to text and images.                                    | 2022.08.21 |

| 05      | Added references for SYSMAP configuration.                             | 2023.03.02 |

| 06      | Added content related to multi-cluster subsystems.                     | 2023.03.07 |

| 07      | Added content related to RV debug.                                     | 2023.06.06 |

| 08      | Added content related to vector module v1.0 and updated manual version | 2023.08.01 |

|         | to R2S0.                                                               |            |

| 09      | Added content related to C920V2 and updated manual version to R2S0. $$ | 2023.09.01 |

| 10      | Updated content related to Vector, added description for DVM, and up-  | 2023.11.16 |

|         | dated manual version to R2S1.                                          |            |

| 11      | Modified the description of Secure Debug.                              | 2024.03.08 |

| 12      | Update PMU description.                                                | 2024.04.25 |

| 13      | Added mseccfg register.                                                | 2024.05.09 |

| 14      | Updated the outstanding capability of the master device interface      | 2024.05.11 |

| 15      | Updated C920 programming model, instruction set version description    | 2024.05.30 |

## Xuantie-C920R2S1-User-Manual

| 1 | Ove | rview                                                                                                                        | 1  |

|---|-----|------------------------------------------------------------------------------------------------------------------------------|----|

|   | 1.1 | $Introduction  \dots $ | 1  |

|   | 1.2 | Features                                                                                                                     | 1  |

|   |     | 1.2.1 Key Architectural Features of C920MP                                                                                   | 1  |

|   |     | 1.2.2 Key Features of C920 Core                                                                                              | 2  |

|   |     | 1.2.3 Key Features of Vector Computing Unit                                                                                  | 3  |

|   | 1.3 | Configurable Options                                                                                                         | 3  |

|   | 1.4 | XuanTie Extended Architecture                                                                                                | 4  |

|   | 1.5 | Version Compatibility                                                                                                        | 4  |

|   | 1.6 | Naming Conventions                                                                                                           | 6  |

|   |     | 1.6.1 Terms                                                                                                                  | 8  |

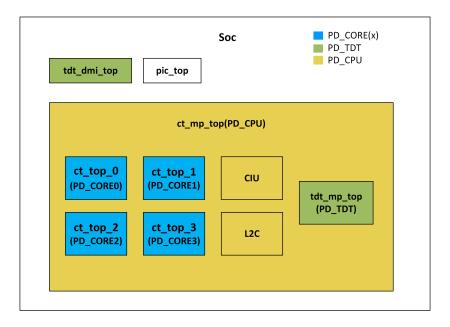

| 2 | C92 | OMP Overview                                                                                                                 | 9  |

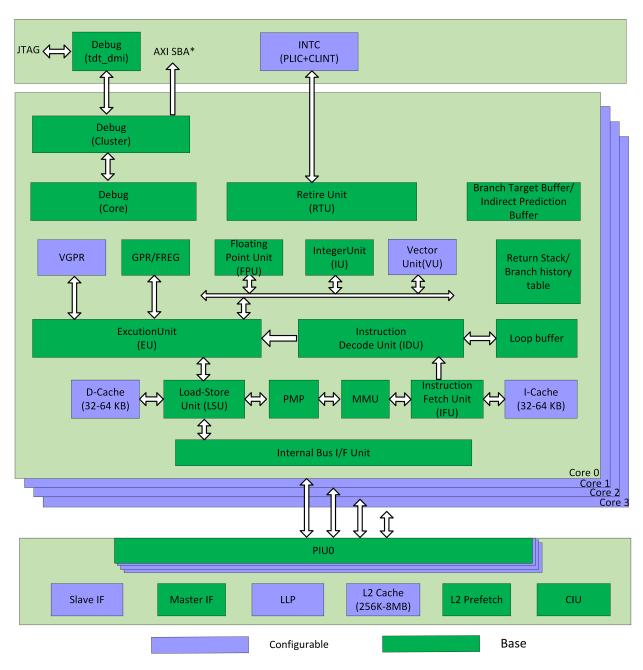

|   | 2.1 | Structure Diagram                                                                                                            | 9  |

|   | 2.2 | In-core Subsystems                                                                                                           | 11 |

|   |     | 2.2.1 IFU                                                                                                                    | 11 |

|   |     | 2.2.2 IDU                                                                                                                    | 11 |

|   |     | 2.2.3 Execution Unit                                                                                                         | 11 |

|   |     | 2.2.4 LSU                                                                                                                    | 12 |

|   |     | 2.2.5 RTU                                                                                                                    | 12 |

|   |     | 2.2.6 MMU                                                                                                                    | 12 |

|   |     | 2.2.7 PMP                                                                                                                    | 12 |

|   | 2.3 | Multi-core Subsystems                                                                                                        | 12 |

|   |     | 2.3.1 CIU                                                                                                                    | 12 |

|   |     | 2.3.2 L2 cache                                                                                                               | 13 |

|   |     | 2.3.3 Master Device Interface                                                                                                | 13 |

|   |     | 2.3.4 DCP                                                                                                                    | 13 |

|   |     | 2.3.5 LLP                                                                                                                    |    |

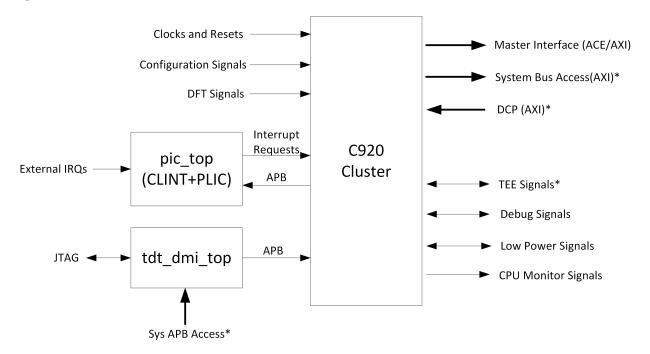

|   | 2.4 | Multi-cluster Subsystem                                                                                                      |    |

|   |     | 2.4.1 PIC                                                                                                                    |    |

|   |     |                                                                                                                              |    |

|   |      | 2.4.2      | Timer                                                                |

|---|------|------------|----------------------------------------------------------------------|

|   |      | 2.4.3      | Debugging System                                                     |

|   | 2.5  | Interfa    | ce Overview                                                          |

| 3 | Inst | ruction    | 1 Sets                                                               |

|   | 3.1  | RV Ba      | se Instruction Sets                                                  |

|   |      | 3.1.1      | Integer Instruction Set (RV64I)                                      |

|   |      | 3.1.2      | Multiplication and Division Instructions (RV64M) Set                 |

|   |      | 3.1.3      | Atomic Instruction Set (RV64A)                                       |

|   |      | 3.1.4      | Single-precision Floating-point Instruction Set (RV64F)              |

|   |      | 3.1.5      | Double-Precision Floating-Point Instruction Set                      |

|   |      | 3.1.6      | Compressed Instruction Set (RV64C)                                   |

|   |      | 3.1.7      | Vector Instruction Set (RV64V)                                       |

|   | 3.2  | XuanT      | Tie Extended Instruction Set                                         |

|   |      | 3.2.1      | Arithmetic Operation Instructions                                    |

|   |      | 3.2.2      | Bit Operation Instructions                                           |

|   |      | 3.2.3      | Memory Access Instructions                                           |

|   |      | 3.2.4      | Cache Instructions                                                   |

|   |      | 3.2.5      | Multi-core Synchronization Instructions                              |

|   |      | 3.2.6      | Half-precision Floating-point Instructions                           |

|   |      | 0.2.0      | Processor 1 reasons point theoreticals 1                             |

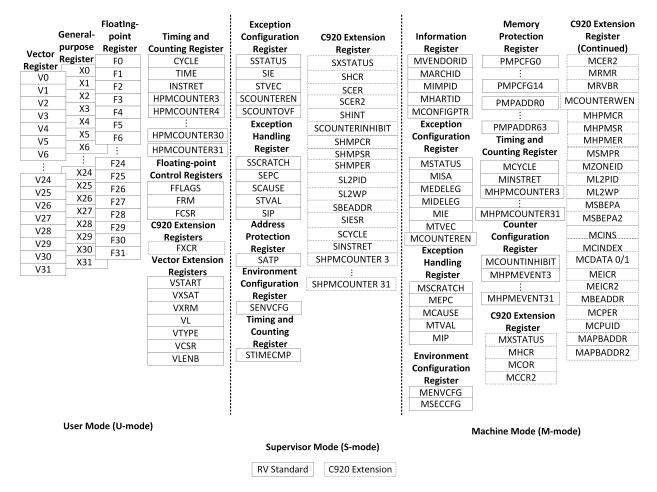

| 4 | CPU  | J Mod      | e and Register 32                                                    |

|   | 4.1  | CPU I      | Mode                                                                 |

|   | 4.2  | Regist     | er View                                                              |

|   | 4.3  | Genera     | al-purpose Registers                                                 |

|   | 4.4  | Floatin    | ng-point Registers                                                   |

|   |      | 4.4.1      | Transfer Data between Floating-point and General-purpose Registers   |

|   |      | 4.4.2      | Maintain the Consistency of Register Precision                       |

|   | 4.5  | Vector     | Register                                                             |

|   |      | 4.5.1      | Transfer Data Between Vector Registers and General-Purpose Registers |

|   |      | 4.5.2      | Transfer Data between Vector Registers and Floating-point Registers  |

|   | 4.6  | System     | Control Registers                                                    |

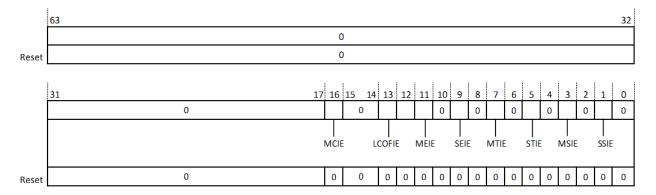

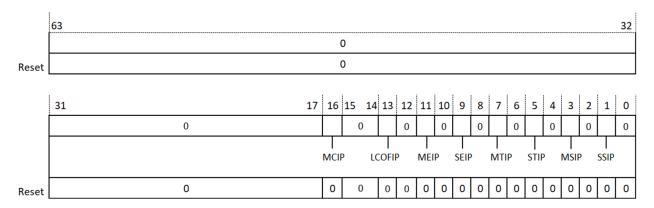

|   |      | 4.6.1      | Standard Control Registers                                           |

|   |      | 4.6.2      | Extended Control Registers                                           |

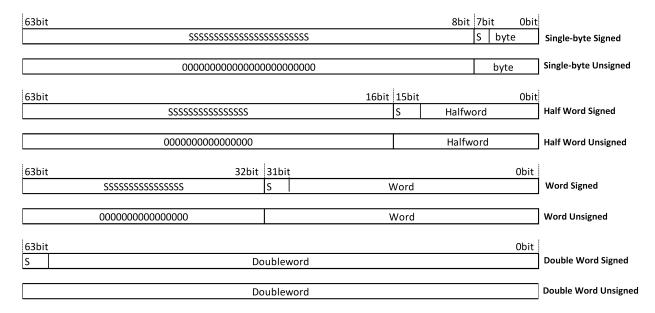

|   | 4.7  | Data I     | Format                                                               |

|   |      | 4.7.1      | Integer Data Format                                                  |

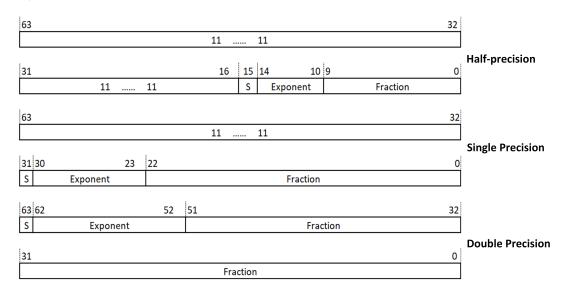

|   |      | 4.7.2      | Floating-point Data Format                                           |

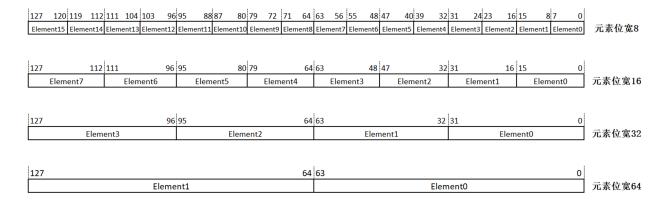

|   |      | 4.7.3      | Vector Data Format                                                   |

|   | 4.8  | Big-en     | dian and Little-endian                                               |

| ۲ | 17   | 4 <b>:</b> | and Interment                                                        |

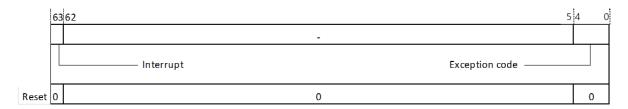

| 5 | 5.1  | _          | and Interrupt         48           dew                               |

|   |      |            |                                                                      |

|   | 5.2  | _          |                                                                      |

|   |      | 5.2.1      | Exception Handling                                                   |

|   |      | 5.2.2      | Exception Return                                                     |

|   |      | 5.2.3      | Imprecise Exceptions                                                 |

|   | 5.3               | Interru                                                                                                                                                                               | pt                                                                                                                                                                                                                                                                                                                                            | 48                                                                               |

|---|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|   |                   | 5.3.1                                                                                                                                                                                 | Interrupt Priorities                                                                                                                                                                                                                                                                                                                          | 48                                                                               |

|   |                   | 5.3.2                                                                                                                                                                                 | Interrupt Response                                                                                                                                                                                                                                                                                                                            | 49                                                                               |

|   |                   | 5.3.3                                                                                                                                                                                 | Interrupt Return                                                                                                                                                                                                                                                                                                                              | 49                                                                               |

| 0 | 7. /T             | 7.                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                               | -0                                                                               |

| 6 |                   | nory N                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                               | 50                                                                               |

|   | 6.1               |                                                                                                                                                                                       | ew                                                                                                                                                                                                                                                                                                                                            |                                                                                  |

|   |                   | 6.1.1                                                                                                                                                                                 | Memory Attributes                                                                                                                                                                                                                                                                                                                             |                                                                                  |

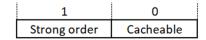

|   |                   | 6.1.2                                                                                                                                                                                 | Memory Ordering Model                                                                                                                                                                                                                                                                                                                         |                                                                                  |

|   |                   | 6.1.3                                                                                                                                                                                 | SYSMAP Configuration Reference                                                                                                                                                                                                                                                                                                                |                                                                                  |

|   | 6.2               | MMU                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

|   |                   | 6.2.1                                                                                                                                                                                 | MMU Overview                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

|   |                   | 6.2.2                                                                                                                                                                                 | TLB Organization                                                                                                                                                                                                                                                                                                                              |                                                                                  |

|   |                   | 6.2.3                                                                                                                                                                                 | Address Translation Process                                                                                                                                                                                                                                                                                                                   | 54                                                                               |

|   |                   | 6.2.4                                                                                                                                                                                 | System Control Registers                                                                                                                                                                                                                                                                                                                      |                                                                                  |

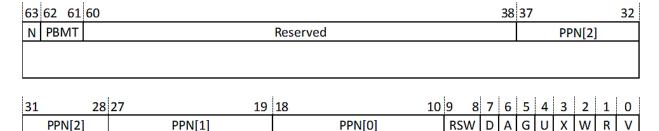

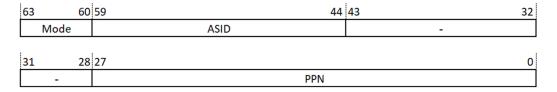

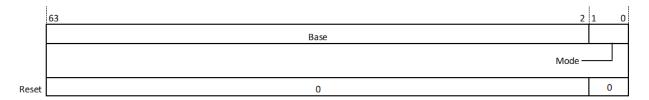

|   |                   |                                                                                                                                                                                       | 6.2.4.1 MMU Address Translation Register (SATP)                                                                                                                                                                                                                                                                                               | 57                                                                               |

|   | 6.3               | MMU                                                                                                                                                                                   | Parity Check                                                                                                                                                                                                                                                                                                                                  | 58                                                                               |

|   | 6.4               | PMP                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

|   |                   | 6.4.1                                                                                                                                                                                 | PMP Overview                                                                                                                                                                                                                                                                                                                                  | 58                                                                               |

|   |                   | 6.4.2                                                                                                                                                                                 | PMP Control Registers                                                                                                                                                                                                                                                                                                                         | 58                                                                               |

|   |                   |                                                                                                                                                                                       | 6.4.2.1 PMPCFG Register                                                                                                                                                                                                                                                                                                                       | 58                                                                               |

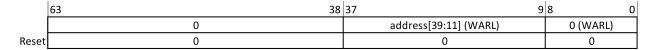

|   |                   |                                                                                                                                                                                       | 6.4.2.2 PMPADDR Register                                                                                                                                                                                                                                                                                                                      | 61                                                                               |

|   | 6.5               | Memo                                                                                                                                                                                  | ry Access Order                                                                                                                                                                                                                                                                                                                               | 61                                                                               |

|   |                   |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

| 7 | Mor               | nory S                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                               | 62                                                                               |

| 7 |                   | -                                                                                                                                                                                     | ubsystem                                                                                                                                                                                                                                                                                                                                      | <b>62</b>                                                                        |

| 7 | 7.1               | Memo                                                                                                                                                                                  | ubsystem ry Subsystem Overview                                                                                                                                                                                                                                                                                                                | 62                                                                               |

| 7 |                   | Memor                                                                                                                                                                                 | ubsystem  ry Subsystem Overview                                                                                                                                                                                                                                                                                                               | 62<br>62                                                                         |

| 7 | 7.1               | Memo:<br>L1 I-C<br>7.2.1                                                                                                                                                              | ubsystem  ry Subsystem Overview                                                                                                                                                                                                                                                                                                               | 62<br>62<br>62                                                                   |

| 7 | 7.1               | Memor<br>L1 I-C<br>7.2.1<br>7.2.2                                                                                                                                                     | ubsystem ry Subsystem Overview ache Overview Branch Prediction                                                                                                                                                                                                                                                                                | 62<br>62<br>62<br>63                                                             |

| 7 | 7.1               | Memor<br>L1 I-C<br>7.2.1<br>7.2.2<br>7.2.3                                                                                                                                            | ubsystem ry Subsystem Overview                                                                                                                                                                                                                                                                                                                | 62<br>62<br>62<br>63<br>63                                                       |

| 7 | 7.1               | Memor<br>L1 I-C<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4                                                                                                                                   | ubsystem  ry Subsystem Overview  ache Overview  Branch Prediction  Loop Acceleration Buffer  Branch History Table                                                                                                                                                                                                                             | 62<br>62<br>63<br>63<br>63                                                       |

| 7 | 7.1               | Memor<br>L1 I-C<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5                                                                                                                          | ubsystem ry Subsystem Overview                                                                                                                                                                                                                                                                                                                | 62<br>62<br>63<br>63<br>63                                                       |

| 7 | 7.1               | Memor<br>L1 I-C<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6                                                                                                                 | ubsystem ry Subsystem Overview ache Overview Branch Prediction Loop Acceleration Buffer Branch History Table Branch Jump Target Predictor Indirect Branch Predictor                                                                                                                                                                           | 62<br>62<br>63<br>63<br>63<br>64                                                 |

| 7 | 7.1               | Memor<br>L1 I-C<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7                                                                                                        | ubsystem  ry Subsystem Overview  ache Overview  Branch Prediction  Loop Acceleration Buffer  Branch History Table  Branch Jump Target Predictor  Indirect Branch Predictor  Return Address Predictor                                                                                                                                          | 62<br>62<br>63<br>63<br>63<br>64<br>64                                           |

| 7 | 7.1<br>7.2        | Memor<br>L1 I-C<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8                                                                                               | ubsystem ry Subsystem Overview ache Overview Branch Prediction Loop Acceleration Buffer Branch History Table Branch Jump Target Predictor Indirect Branch Predictor Return Address Predictor Fast Jump Target Predictor                                                                                                                       | 62<br>62<br>63<br>63<br>63<br>64<br>64<br>65                                     |

| 7 | 7.1               | Memor<br>L1 I-C<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>L1 D-C                                                                                     | ubsystem ry Subsystem Overview ache Overview Branch Prediction Loop Acceleration Buffer Branch History Table Branch Jump Target Predictor Indirect Branch Predictor Return Address Predictor Fast Jump Target Predictor                                                                                                                       | 62<br>62<br>63<br>63<br>63<br>64<br>64<br>65                                     |

| 7 | 7.1<br>7.2        | Memor<br>L1 I-C<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>L1 D-C<br>7.3.1                                                                            | ubsystem  ry Subsystem Overview ache Overview Branch Prediction Loop Acceleration Buffer Branch History Table Branch Jump Target Predictor Indirect Branch Predictor Return Address Predictor Fast Jump Target Predictor Cache Overview                                                                                                       | 62<br>62<br>63<br>63<br>63<br>64<br>64<br>65<br>65                               |

| 7 | 7.1<br>7.2        | Memor<br>L1 I-C<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>L1 D-C<br>7.3.1<br>7.3.2                                                                   | ubsystem ry Subsystem Overview ache Overview Branch Prediction Loop Acceleration Buffer Branch History Table Branch Jump Target Predictor Indirect Branch Predictor Return Address Predictor Fast Jump Target Predictor Cache Overview L1 D-Cache Coherence                                                                                   | 62<br>62<br>63<br>63<br>63<br>64<br>64<br>65<br>65<br>65                         |

| 7 | 7.1 7.2           | Memor<br>L1 I-C<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>L1 D-C<br>7.3.1<br>7.3.2<br>7.3.3                                                          | ubsystem ry Subsystem Overview ache Overview Branch Prediction Loop Acceleration Buffer Branch History Table Branch Jump Target Predictor Indirect Branch Predictor Return Address Predictor Fast Jump Target Predictor Cache Overview L1 D-Cache Coherence Exclusive Access                                                                  | 62<br>62<br>63<br>63<br>63<br>64<br>64<br>65<br>65<br>65<br>66                   |

| 7 | 7.1<br>7.2        | Memor<br>L1 I-C<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>L1 D-C<br>7.3.1<br>7.3.2<br>7.3.3<br>L2 Car                                                | ubsystem ry Subsystem Overview ache Overview Branch Prediction Loop Acceleration Buffer Branch History Table Branch Jump Target Predictor Indirect Branch Predictor Return Address Predictor Fast Jump Target Predictor Cache Overview L1 D-Cache Coherence Exclusive Access                                                                  | 62<br>62<br>63<br>63<br>63<br>64<br>64<br>65<br>65<br>65<br>66<br>66             |

| 7 | 7.1 7.2           | Memor<br>L1 I-C<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>L1 D-C<br>7.3.1<br>7.3.2<br>7.3.3<br>L2 Cac<br>7.4.1                                       | ubsystem ry Subsystem Overview . ache Overview Branch Prediction Loop Acceleration Buffer Branch History Table Branch Jump Target Predictor Indirect Branch Predictor Return Address Predictor Fast Jump Target Predictor Cache Overview L1 D-Cache Coherence Exclusive Access che L2 Cache Overview                                          | 62<br>62<br>63<br>63<br>63<br>64<br>64<br>65<br>65<br>65<br>66<br>66<br>66       |

| 7 | 7.1 7.2           | Memor<br>L1 I-C<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>L1 D-C<br>7.3.1<br>7.3.2<br>7.3.3<br>L2 Cac<br>7.4.1                                       | ubsystem ry Subsystem Overview ache Overview Branch Prediction Loop Acceleration Buffer Branch History Table Branch Jump Target Predictor Indirect Branch Predictor Return Address Predictor Fast Jump Target Predictor Cache Overview L1 D-Cache Coherence Exclusive Access the L2 Cache Overview L2 D-Cache Coherence                       | 62<br>62<br>63<br>63<br>63<br>64<br>64<br>65<br>65<br>65<br>66<br>66<br>66<br>66 |

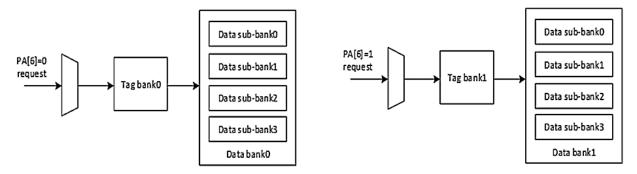

| 7 | 7.1 7.2           | Memori<br>L1 I-C<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>L1 D-C<br>7.3.1<br>7.3.2<br>7.3.3<br>L2 Cac<br>7.4.1<br>7.4.2                             | ubsystem ry Subsystem Overview ache Overview Branch Prediction Loop Acceleration Buffer Branch History Table Branch Jump Target Predictor Indirect Branch Predictor Return Address Predictor Fast Jump Target Predictor Cache Overview L1 D-Cache Coherence Exclusive Access che L2 Cache Overview L2 D-Cache Coherence Structure             | 62<br>62<br>63<br>63<br>63<br>64<br>65<br>65<br>65<br>66<br>66<br>67             |

| 7 | 7.1<br>7.2<br>7.3 | Memor<br>L1 I-C<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>L1 D-C<br>7.3.1<br>7.3.2<br>7.3.3<br>L2 Cac<br>7.4.1<br>7.4.2<br>7.4.3                     | ubsystem ry Subsystem Overview ache Overview Branch Prediction Loop Acceleration Buffer Branch History Table Branch Jump Target Predictor Indirect Branch Predictor Return Address Predictor Fast Jump Target Predictor Cache Overview L1 D-Cache Coherence Exclusive Access che L2 Cache Overview L2 D-Cache Coherence Structure RAM Latency | 622<br>622<br>633<br>633<br>634<br>644<br>655<br>656<br>666<br>667<br>677<br>688 |

| 7 | 7.1 7.2           | Memori<br>L1 I-C<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>L1 D-C<br>7.3.1<br>7.3.2<br>7.3.3<br>L2 Cac<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.4<br>Accele | ubsystem ry Subsystem Overview ache Overview Branch Prediction Loop Acceleration Buffer Branch History Table Branch Jump Target Predictor Indirect Branch Predictor Return Address Predictor Fast Jump Target Predictor Cache Overview L1 D-Cache Coherence Exclusive Access che L2 Cache Overview L2 D-Cache Coherence Structure             | 62<br>62<br>63<br>63<br>63<br>64<br>64<br>65<br>65<br>66<br>66<br>67<br>67<br>68 |

|    |        | 7.5.2   | Multi-channel Data Prefetch of L1 D-Cache                 | 70  |

|----|--------|---------|-----------------------------------------------------------|-----|

|    |        | 7.5.3   | L1 Adaptive Write Allocation Mechanism                    | 70  |

|    |        | 7.5.4   | L2 Prefetch Mechanism                                     | 70  |

|    | 7.6    | L1/L2   | Cache Operation Instruction and Register                  | 71  |

|    |        | 7.6.1   | Extented Register of L1 Cache                             | 71  |

|    |        | 7.6.2   | Extented Register of L2 Cache                             | 71  |

|    |        | 7.6.3   | L1/L2 Cache Operation Instruction                         | 71  |

|    | 7.7    | L1/L2   | Cache Protection Mechanism                                | 72  |

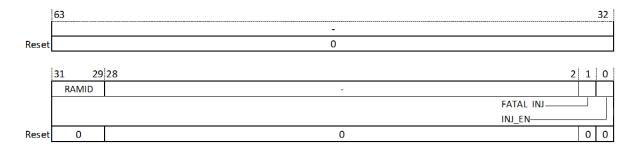

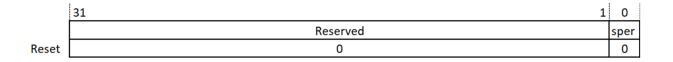

|    |        | 7.7.1   | L1 I-Cache Parity Check                                   | 73  |

|    |        | 7.7.2   | L1 D-Cache ECC Check                                      | 73  |

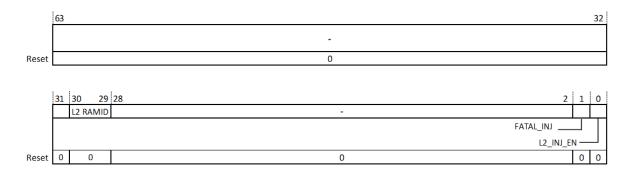

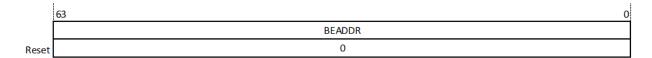

|    |        | 7.7.3   | L2 ECC Check                                              | 74  |

| 8  | Vect   | or Cor  | nputation                                                 | 75  |

|    | 8.1    | suppor  | ting Version                                              | 75  |

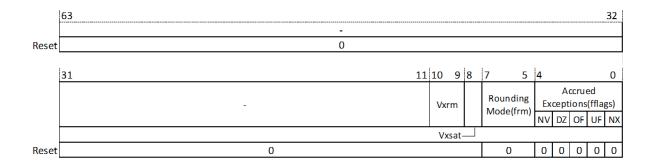

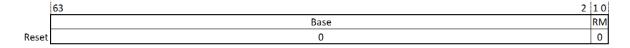

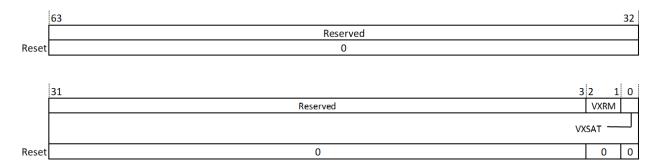

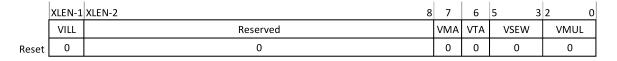

|    | 8.2    | Vector  | Programming Model                                         | 75  |

|    | 8.3    |         |                                                           | 75  |

|    | 8.4    |         |                                                           | 76  |

| 9  | Soci   | ırity D | osign                                                     | 78  |

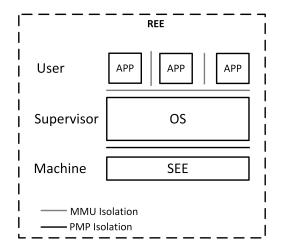

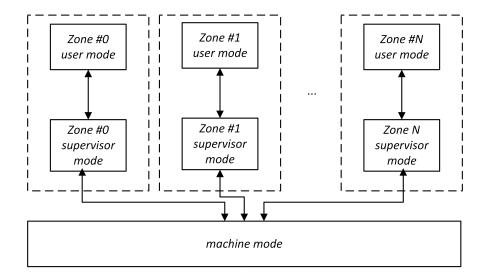

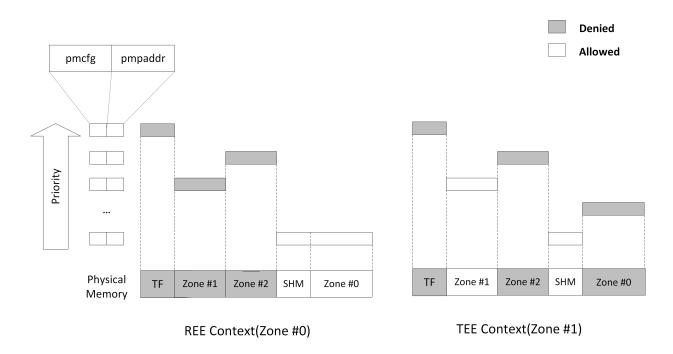

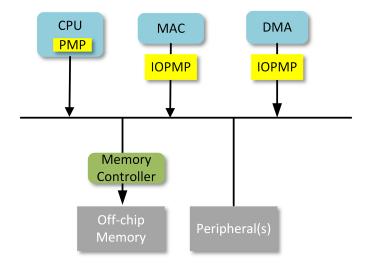

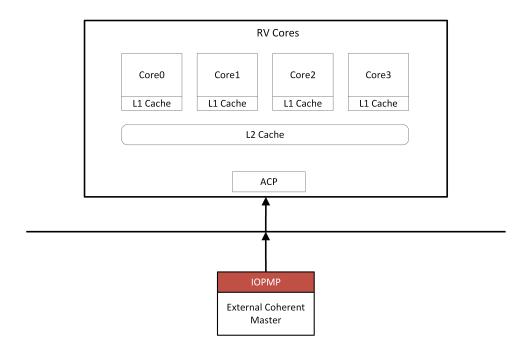

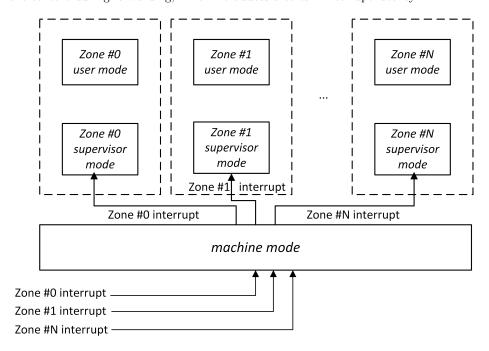

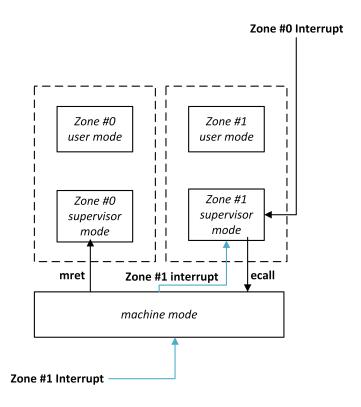

| 9  | 9.1    | -       |                                                           | 78  |

|    | 9.2    |         |                                                           | 78  |

|    | 9.2    |         | a Security Architecture                                   | 80  |

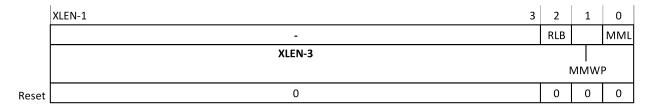

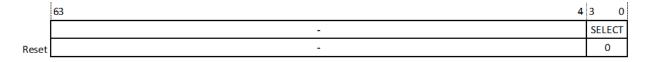

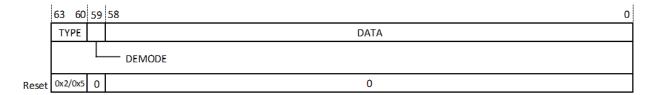

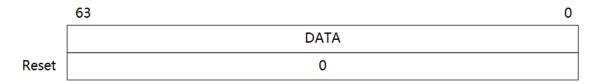

|    | 9.5    | 9.3.1   |                                                           |     |

|    |        |         |                                                           | 80  |

|    |        | 9.3.2   | Secure Interrupts                                         | 84  |

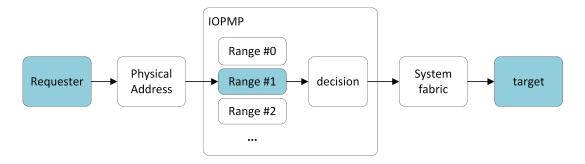

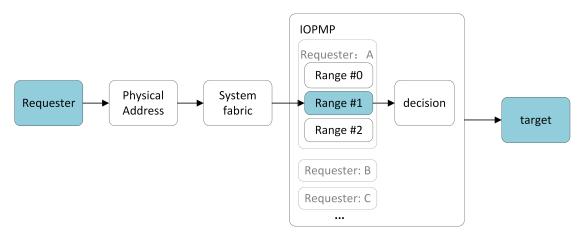

|    |        | 9.3.3   | Secure Access Control                                     | 87  |

|    |        | 9.3.4   | Secure Debug                                              | 88  |

| 10 | ) Inte | rrupt ( | Controller                                                | 89  |

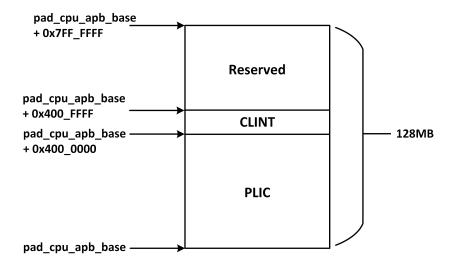

|    | 10.1   | CLINT   | TInterrupt Controller                                     | 89  |

|    |        | 10.1.1  | CLINT Register Address Mapping                            | 89  |

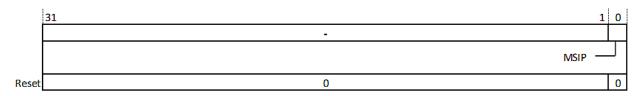

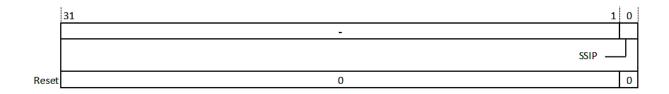

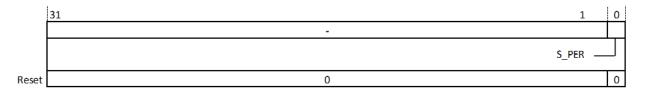

|    |        | 10.1.2  | Software Interrupts                                       | 96  |

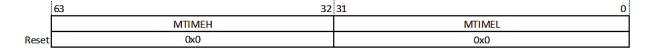

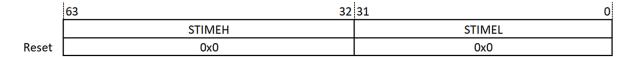

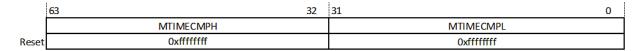

|    |        | 10.1.3  | Timer                                                     | 97  |

|    |        | 10.1.4  | Timer Interrupts                                          | 97  |

|    | 10.2   | PLIC    |                                                           | 98  |

|    |        | 10.2.1  | Arbitration of Interrupts                                 | 99  |

|    |        | 10.2.2  | Request and Response of Interrupts                        | 99  |

|    |        | 10.2.3  | Interrupt Completion                                      | 100 |

|    |        | 10.2.4  | PLIC Register Address Mapping                             | 100 |

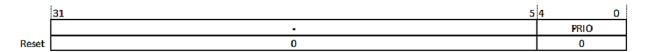

|    |        | 10.2.5  | Interrupt Priority Configuration Register (PLIC_PRIO)     | 105 |

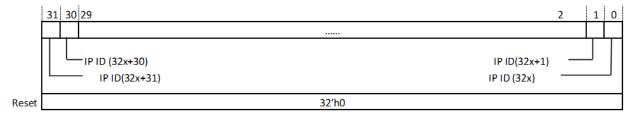

|    |        | 10.2.6  | Interrupt Pending Register (PLIC_IP)                      | 105 |

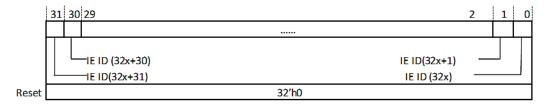

|    |        | 10.2.7  | Interrupt Enable Register (PLIC_IE)                       | 106 |

|    |        | 10.2.8  | PLIC Permission Control Register (PLIC_CTRL)              | 106 |

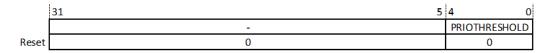

|    |        | 10.2.9  | PLIC Threshold Register (PLIC_TH)                         |     |

|    |        |         | Interrupt Response/Completion Register (PLIC_CLAIM)       |     |

|    | 10.3   |         | core Interrupts                                           |     |

|    |        |         | Multiple Cores Respond to External Interrupts in Parallel |     |

|    |                                              | 10.3.2 Send Software Interrupts across Cores                  | 108                                                                          |

|----|----------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------|

| 11 | Bus                                          | Interface 1                                                   | 09                                                                           |

|    | 11.1                                         | Master Device Interface                                       | 109                                                                          |

|    |                                              | 11.1.1 Features of the Master Device Interface                | 109                                                                          |

|    |                                              | 11.1.2 Outstanding Capability of the Master Device Interface  | 109                                                                          |

|    |                                              | 11.1.3 Supported Transmission Types                           |                                                                              |

|    |                                              | 11.1.4 Supported Response Types                               | 111                                                                          |

|    |                                              | 11.1.5 Behavior in Different Bus Responses                    |                                                                              |

|    |                                              | 11.1.6 Signals Supported by the Master Device Interface       |                                                                              |

|    |                                              | 11.1.7 Supported Coherency Transaction Types                  |                                                                              |

|    | 11.2                                         |                                                               |                                                                              |

|    |                                              | 11.2.1 Features of DCP                                        |                                                                              |

|    |                                              | 11.2.2 Supported Transfer Types                               |                                                                              |

|    |                                              | 11.2.3 L2 cache Allocation Behavior under Different Transfers |                                                                              |

|    |                                              | 11.2.4 Supported Response Types                               |                                                                              |

|    |                                              | 11.2.5 Responses under Different Behaviors                    |                                                                              |

|    |                                              | 11.2.6 DCP Signals                                            |                                                                              |

|    | 11.3                                         |                                                               |                                                                              |

|    | 11.0                                         | 11.3.1 The Features of LLP                                    |                                                                              |

|    |                                              | 11.3.2 The Outstanding Capability of LLP                      |                                                                              |

|    |                                              | 11.3.3 Supported Transfer Types                               |                                                                              |

|    |                                              | 11.3.4 Supported Response Types                               |                                                                              |

|    |                                              | Thosa cappointed recipolise Types                             |                                                                              |

| 12 | Deb                                          | $_{ m ug}$                                                    | <b>2</b> 5                                                                   |

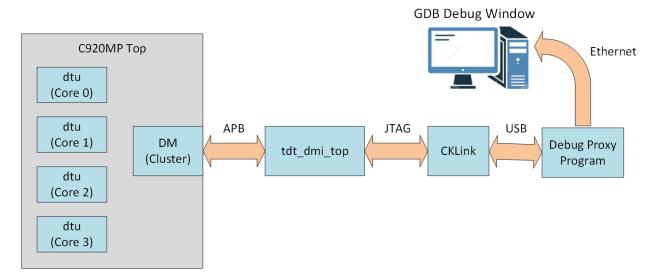

|    | 12.1                                         | Features of Debug Unit                                        | 125                                                                          |

|    | 12.2                                         | Configuration of Debug Resources                              | 126                                                                          |

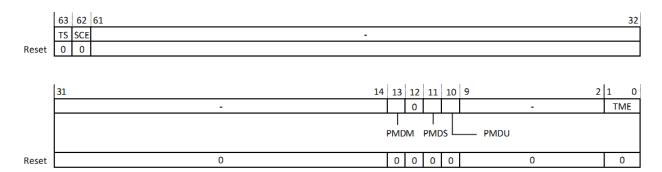

| 13 | Pow                                          | er Management 1                                               | 28                                                                           |

|    |                                              | Power Domain                                                  |                                                                              |

|    |                                              | Overview of Low-power Modes                                   |                                                                              |

|    |                                              | •                                                             |                                                                              |

|    | 10.0                                         | Core WFI Process                                              | 129                                                                          |

|    | 13.4                                         | Core WFI Process                                              |                                                                              |

|    |                                              | Single-Core Power-Down Process                                | 130                                                                          |

|    | 13.5                                         | Single-Core Power-Down Process                                | L30<br>L31                                                                   |

|    | 13.5<br>13.6                                 | Single-Core Power-Down Process                                | 130<br>131<br>132                                                            |

|    | 13.5                                         | Single-Core Power-Down Process                                | 130<br>131<br>132<br>133                                                     |

|    | 13.5<br>13.6                                 | Single-Core Power-Down Process                                | 130<br>131<br>132<br>133                                                     |

|    | 13.5<br>13.6                                 | Single-Core Power-Down Process                                | 130<br>131<br>132<br>133                                                     |

| 14 | 13.5<br>13.6<br>13.7                         | Single-Core Power-Down Process                                | 130<br>131<br>132<br>133                                                     |

| 14 | 13.5<br>13.6<br>13.7                         | Single-Core Power-Down Process                                | 130<br>131<br>132<br>133<br>133                                              |

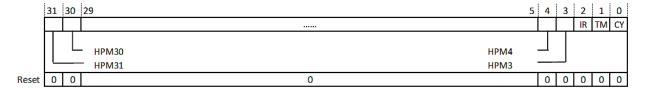

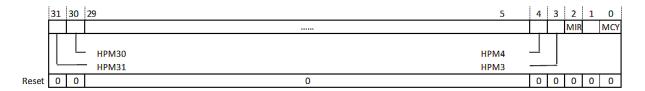

| 14 | 13.5<br>13.6<br>13.7<br>Perf<br>14.1         | Single-Core Power-Down Process                                | 130<br>131<br>132<br>133<br>133<br>134                                       |

| 14 | 13.5<br>13.6<br>13.7<br>Perf<br>14.1         | Single-Core Power-Down Process                                | 130<br>131<br>132<br>133<br>133<br>134<br>134                                |

| 14 | 13.5<br>13.6<br>13.7<br>Perf<br>14.1         | Single-Core Power-Down Process                                | 130<br>131<br>132<br>133<br>133<br>134<br>134                                |

| 14 | 13.5<br>13.6<br>13.7<br>Perf<br>14.1<br>14.2 | Single-Core Power-Down Process                                | 130<br>131<br>132<br>133<br>133<br>134<br>134<br>134                         |

| 14 | 13.5<br>13.6<br>13.7<br>Perf<br>14.1<br>14.2 | Single-Core Power-Down Process                                | 130<br>131<br>132<br>133<br>133<br>134<br>134<br>134<br>135                  |

| 14 | 13.5<br>13.6<br>13.7<br>Perf<br>14.1<br>14.2 | Single-Core Power-Down Process                                | l 30<br>l 31<br>l 32<br>l 33<br>l 33<br>l 34<br>l 34<br>l 34<br>l 35<br>l 35 |

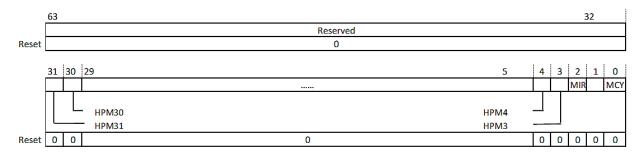

|        | 14.3.3 MHPMCR Register                                                  | 196 |

|--------|-------------------------------------------------------------------------|-----|

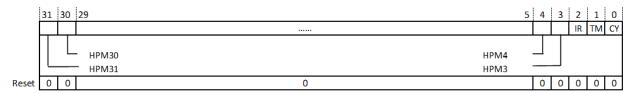

|        | 14.3.4 Mcounterwen Register                                             |     |

|        | 14.3.5 Scounteren Register                                              |     |

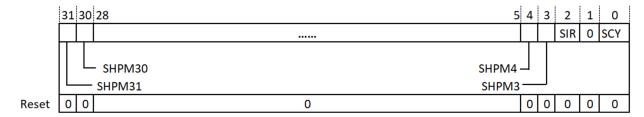

|        | 14.3.6 SHPMINHIBIT Register                                             |     |

|        | 14.3.7 SHPMCR Register                                                  |     |

|        |                                                                         |     |

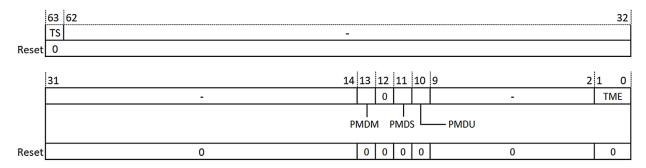

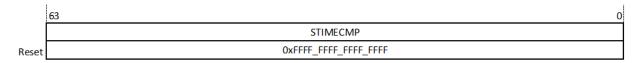

|        | 14.3.8 STIMECMP Register                                                |     |

| 14.4   |                                                                         |     |

|        | 5 Event Counters                                                        |     |

| 14.6   |                                                                         |     |

| 14.0   | 14.6.1 Start Trigger Register                                           |     |

|        | 14.6.2 End Trigger Register                                             |     |

|        | 14.0.2 End frigger Register                                             | 140 |

| 15 Pro | ogram Instances                                                         | 147 |

| 15.    | 1 Optimal CPU Performance Configuration                                 | 147 |

| 15.5   | 2 MMU Setting Instance                                                  | 148 |

| 15.3   | 3 PMP Setting Instance                                                  | 151 |

| 15.4   | 4 Cache Instance                                                        | 152 |

|        | 15.4.1 Cache Enabling Instance                                          | 152 |

|        | 15.4.2 Synchronization Instance between Instruction and Data Caches     | 153 |

|        | 15.4.3 Synchronization Instance between TLB and Data Cache              | 154 |

|        | 15.4.4 L2 Cache Partitioning Feature Configuration                      | 154 |

| 15.    | 5 Multi-core Startup Instance                                           | 155 |

| 15.0   | 6 Synchronization Primitive Instance                                    | 155 |

| 15.    | 7 PLIC Setting Instance                                                 | 156 |

| 15.8   | 8 PMU Setting Instance                                                  | 156 |

| 16 An  | ppendix A Standard Instructions                                         | 158 |

| 16.1   |                                                                         |     |

| 10.    | 16.1.1 ADD——The Signed Add Instruction                                  |     |

|        | 16.1.2 ADDI—The Signed Immediate Add Instruction                        |     |

|        | 16.1.3 ADDIW—The Signed Immediate Add Instruction for the Lower 32 Bits |     |

|        | 16.1.4 ADDW——The Signed Add Instruction for the Lower 32 Bits           |     |

|        | 16.1.5 AND—The Bitwise AND Instruction                                  |     |

|        | 16.1.6 ANDI—The Immediate Bitwise AND Instruction                       |     |

|        | 16.1.7 AUIPC——The Add Upper Immediate to PC Instruction                 |     |

|        | 16.1.8 BEQ—The Branch-if-equal Instruction                              |     |

|        | 16.1.9 BGE——The Signed Branch-if-greater-than-or-equal Instruction      |     |

|        | 16.1.10 BGEU—The Unsigned Branch-if-greater-than-or-equal instruction   |     |

|        | 16.1.11 BLT—The Signed Branch-if-less-than Instruction                  |     |

|        | 16.1.12 BLTU—The Unsigned Branch-if-less-than Instruction               |     |

|        | 16.1.13 BNE——The Branch-if-not-equal Instruction                        |     |

|        | 16.1.14 CSRRC—The Control and Status Register Read/Clear Instruction    |     |

|        | 16.1.15 CSRRCI—The CSR Read/Clear Immediate Instruction                 |     |

|        | 16.1.16 CSRRS——The CSR Read/Set Instruction                             |     |

|        | 16.1.17 CSRRSI—The CSR Read/Set Immediate Instruction                   |     |

|        |                                                                         |     |

| 16.1.18 CSRRW——The CSR Read/Write Instruction                                                                         |

|-----------------------------------------------------------------------------------------------------------------------|

| 16.1.19 CSRRWI——The CSR Read/Write Immediate Instruction                                                              |

| 16.1.20 EBREAK——The Breakpoint Instruction                                                                            |

| 16.1.21 ECALL——The Environment Call Instruction                                                                       |

| 16.1.22 FENCE——The Memory Synchronization Instruction                                                                 |

| 16.1.23 FENCE.I——The Instruction Stream Synchronization Instruction                                                   |

| 16.1.24 JAL——The Instruction for Directly Jumping to a Subroutine                                                     |

| 16.1.25 JALR——The Jump and Link Register Instruction                                                                  |

| 16.1.26 LB——The Signed Extended Byte Load Instruction                                                                 |

| 16.1.27 LBU——The unsigned Extended Byte Load Instruction                                                              |

| 16.1.28 LD——The Doubleword Load Instruction                                                                           |

| 16.1.29 LH——The Signed Extended Halfword Load Instruction                                                             |

| 16.1.30 LHU——The Unsigned Extended Halfword Load Instruction                                                          |

| 16.1.31 LUI——The Upper Immediate Load Instruction                                                                     |

| 16.1.32 LW——The Signed Extended Word Load Instruction                                                                 |

| 16.1.33 LWU——The Unsigned Extended Word Load Instruction                                                              |

| 16.1.34 MRET——The Exception Return Instruction in M-mode                                                              |

| 16.1.35 OR——The Bitwise OR Instruction                                                                                |

| 16.1.36 ORI——The Immediate Bitwise OR Instruction                                                                     |

| 16.1.37 SB——The Byte Store Instruction                                                                                |

| 16.1.38 SD——The Doubleword Store Instruction                                                                          |

| 16.1.39 SFENCE.VMA——The Virtual Memory Synchronization Instruction                                                    |

| 16.1.40 SH——The Halfword Store Instruction                                                                            |

| 16.1.41 SLL——The Logical Left Shift instruction                                                                       |

| 16.1.42 SLLI——The Immediate Logical Left Shift Instruction                                                            |

| 16.1.43 SLLIW——The Immediate Logical Left Shift Instruction on the Lower 32 Bits 179                                  |

| 16.1.44 SLLW——The Logical Left Shift Instruction on the Lower 32 Bits                                                 |

| 16.1.45 SLT——The Signed Set-If-Less-than Instruction                                                                  |

| 16.1.46 SLTI——The Signed Set-If-less-than-Immediate Instruction                                                       |

| $16.1.47 \; \text{SLTIU} - \text{The Unsigned Set-If-less-than-Immediate Instruction} \;\; \dots \;\; \dots \;\; 181$ |

| 16.1.48 SLTU——The Unsigned Set-If-less-than Instruction                                                               |

| 16.1.49 SRA—The Arithmetic Right Shift Instruction                                                                    |

| 16.1.50 SRAI——The Immediate Arithmetic Right Shift Instruction                                                        |

| $16.1.51~\mathrm{SRAIW}$ —The Immediate Arithmetic Right Shift Instruction on the Lower 32 Bits $\dots$ 183           |

| 16.1.52 SRAW——The Arithmetic Right Shift Instruction on the Lower 32 Bits                                             |

| 16.1.53 SRET——The Exception Return Instruction in S-mode                                                              |

| 16.1.54 SRL——The Logical Right Shift Instruction                                                                      |

| 16.1.55 SRLI——The Immediate Logical Right Shift Instruction                                                           |

| 16.1.56 SRLIW——The Immediate Logical Right Shift Instruction on the Lower 32 Bits $185$                               |

| 16.1.57 SRLW——The Logical Right Shift Instruction on the Lower 32 Bits                                                |

| 16.1.58 SUB——The Signed Subtract Instruction                                                                          |

| 16.1.59 SUBW——The Signed Subtract Instruction on the Lower 32 Bits                                                    |

| 16.1.60 SW——The Word Store Instruction                                                                                |

| 16.1.61 WFI—The Instruction for Entering the Low Power Mode                                                           |

| 16.1.62 XOR——The Bitwise XOR Instruction                                                                              |

|      | 16.1.63 | 3 XORI——The Immediate Bitwise XOR Instruction                                                                     | 188 |

|------|---------|-------------------------------------------------------------------------------------------------------------------|-----|

| 16.2 | Appen   | dix A-2 M instructions                                                                                            | 189 |

|      | 16.2.1  | DIV——The Signed Divide Instruction                                                                                | 189 |

|      | 16.2.2  | DIVU—The Unsigned Divide Instruction                                                                              | 189 |

|      | 16.2.3  | DIVUW—The Unsigned Divide Instruction on the Lower 32 Bits                                                        | 190 |

|      | 16.2.4  | DIVW——The Signed Divide Instruction on the Lower 32 Bits                                                          | 190 |

|      | 16.2.5  | MUL—The Signed Multiply Instruction                                                                               | 191 |

|      | 16.2.6  | MULH——The Signed Multiply Upper Bit Extraction Instruction                                                        | 191 |

|      | 16.2.7  | MULHSU——The Signed and Unsigned Multiply Upper Bit Extraction Instruction                                         | 192 |

|      | 16.2.8  | MULHU—The Unsigned Multiply Upper Bit Extraction Instruction                                                      | 192 |

|      | 16.2.9  | MULW——The Signed Multiply Instruction on the Lower 32 Bits                                                        | 193 |

|      | 16.2.10 | REM—The Signed Remainder Instruction                                                                              | 193 |

|      | 16.2.11 | REMU—The Unsigned Remainder Divide Instruction                                                                    | 194 |

|      | 16.2.12 | REMUW—The Unsigned Remainder Divide Instruction on the Lower 32 Bits                                              | 194 |

|      | 16.2.13 | REMW—The Signed Remainder Divide Instruction on the Lower 32 Bits                                                 | 195 |

| 16.3 | Appen   | dix A-3 A Instructions                                                                                            | 195 |

|      | 16.3.1  | AMOADD.D—The Atomic Add Instruction                                                                               | 195 |

|      | 16.3.2  | AMOADD.W——The Atomic Add Instruction on the Lower 32 Bits                                                         | 196 |

|      | 16.3.3  | AMOAND.D—The Atomic Bitwise AND Instruction                                                                       | 197 |

|      | 16.3.4  | AMOAND.W——The Atomic Bitwise AND Instruction on the Lower 32 Bits                                                 | 198 |

|      | 16.3.5  | AMOMAX.D——The Atomic Signed Maximum Instruction on the Lower 32 Bits                                              | 198 |

|      | 16.3.6  | AMOMAX.W——The Atomic Signed Maximum Instruction on the Lower 32 Bits                                              | 199 |

|      | 16.3.7  | AMOMAXU.D——The Atomic Unsigned Maximum Instruction                                                                | 200 |

|      | 16.3.8  | AMOMAXU.W——The Atomic Unsigned Maximum Instruction on the Lower 32 Bits                                           | 201 |

|      | 16.3.9  | AMOMIN.D——The Atomic Signed Minimum Instruction                                                                   | 202 |

|      | 16.3.10 | AMOMIN.W——The Atomic Signed Minimum Instruction on the Lower 32 Bits                                              | 203 |

|      | 16.3.11 | AMOMINU.D——The Atomic Unsigned Minimum Instruction                                                                | 203 |

|      | 16.3.12 | 2 AMOMINU.W——The Atomic Unsigned Minimum Instruction on the Lower 32 Bits                                         | 204 |

|      | 16.3.13 | 3 AMOOR.D——The Atomic Bitwise OR Instruction                                                                      | 205 |

|      | 16.3.14 | AMOOR.W——The Atomic Bitwise OR Instruction on the Lower 32 Bits                                                   | 206 |

|      | 16.3.15 | 5 AMOSWAP.D——The Atomic Swap Instruction                                                                          | 207 |

|      | 16.3.16 | 3 AMOSWAP.W——The Atomic Swap Instruction on the Lower 32 Bits                                                     | 207 |

|      | 16.3.17 | AMOXOR.D——The Atomic Bitwise XOR Instruction                                                                      | 208 |

|      | 16.3.18 | 3 AMOXOR.W——The Atomic Bitwise XOR Instruction on the Lower 32 Bits                                               | 209 |

|      | 16.3.19 | LR.D——The Doubleword Load-reserved Instruction                                                                    | 210 |

|      | 16.3.20 | LR.W——The Word Load-reserved Instruction                                                                          | 211 |

|      | 16.3.21 | SC.D—The Doubleword Conditional Store Instruction                                                                 | 211 |

|      | 16.3.22 | 2 SC.W——The Word Conditional Store Instruction                                                                    | 212 |

| 16.4 | Appen   | dix A-4 F instructions                                                                                            | 213 |

|      | 16.4.1  | FADD.S——The Single-precision Floating-point Add Instruction                                                       | 213 |

|      | 16.4.2  | $\label{eq:fclass} \begin{tabular}{ll} FCLASS.S The Single-precision Floating-point Classification Instruction }$ | 214 |

|      | 16.4.3  | FCVT.L.S——The Instruction to Convert a Single-precision Floating-point Number to a                                |     |

|      |         | Signed Long Integer                                                                                               | 215 |

|      | 16.4.4  | FCVT.LU.S—The Instruction to Convert a Single-precision Floating-point Number to a                                |     |

|      |         | Unsigned Long Integer                                                                                             | 216 |

|      | 16.4.5  | FCVT.S.L——The Instruction to Convert a Signed Long Integer to a Single-precision Floating-           |     |

|------|---------|------------------------------------------------------------------------------------------------------|-----|

|      |         | point Number                                                                                         | 217 |

|      | 16.4.6  | FCVT.S.LU——The Instruction to Convert a Unsigned Long Integer to a Single-precision                  |     |

|      |         | Floating-point Number                                                                                | 218 |

|      | 16.4.7  | FCVT.S.W——The Instruction to Convert a Signed Integer to a Single-precision Floating-                |     |

|      |         | point Number                                                                                         | 219 |

|      | 16.4.8  | FCVT.S.WU—The Instruction to Convert a Unsigned Integer to a Single-precision Floating-              |     |

|      |         | point Number                                                                                         | 220 |

|      | 16.4.9  | FCVT.W.S—The Instruction to Convert a Single-precision Floating-point Number to a                    |     |

|      |         | Signed Integer                                                                                       | 220 |

|      | 16.4.10 | FCVT.WU.S—The Instruction to Convert a Single-precision Floating-point Number to a                   |     |

|      |         | Unsigned Integer                                                                                     | 221 |

|      | 16.4.11 | FDIV.S—The Single-precision Floating-point Divide instruction                                        | 222 |

|      | 16.4.12 | FEQ.S—The Single-precision Floating-point Compare Equal Instruction                                  | 223 |

|      | 16.4.13 | FLE.S—The Single-precision Floating-point Compare Less than or Equal to Instruction                  | 224 |

|      | 16.4.14 | FLT.S—The Single-precision Floating-point Compare Less than Instruction                              | 224 |

|      | 16.4.15 | FLW—The Single-precision Floating-point Load Instruction                                             | 225 |

|      | 16.4.16 | FMADD.S—The Single-precision Floating-point Multiply-add Instruction                                 | 225 |

|      | 16.4.17 | FMAX.S—The Single-Precision Floating-Point Maxmum Instruction                                        | 226 |

|      | 16.4.18 | FMIN.S—The Single-Precision Floating-Point Minimum Instruction                                       | 227 |

|      | 16.4.19 | FMSUB.S—The Single-precision Floating-point Multiply-subtract Instruction                            | 227 |

|      | 16.4.20 | FMUL.S—The Single-precision Floating-point Multiply Instruction                                      | 228 |

|      | 16.4.21 | FMV.W.X—The Single-precision Floating-point Write Transfer Instruction                               | 229 |

|      | 16.4.22 | FMV.X.W——The Single-precision Floating-point Register Read Transfer Instruction                      | 230 |

|      | 16.4.23 | FNMADD.S——The Single-precision Floating-point Negate-(Multiply-add) Instruction                      | 230 |

|      | 16.4.24 | ${\tt FNMSUB.SThe\ Single-precision\ Floating-point\ Negate-(Multiply-subtract)\ Instruction\ .\ .}$ | 231 |

|      | 16.4.25 | FSGNJ.S—The Single-precision Floating-point Sign-injection Instruction                               | 232 |

|      | 16.4.26 | FSGNJN.S—The Single-precision Floating-point Negate Sign-injection Instruction                       | 232 |

|      | 16.4.27 | FSGNJX.S—The Single-precision Floating-point XOR Sign-injection Instruction                          | 233 |

|      | 16.4.28 | FSQRT.S—The Single-precision Floating-point Square-root Instruction                                  | 234 |

|      | 16.4.29 | FSUB.S—The Single-precision Floating-point Subtract Instruction                                      | 234 |

|      | 16.4.30 | FSW—The Single-precision Floating-point Store Instruction                                            | 235 |

| 16.5 | Append  | dix A-5 D Instructions                                                                               | 236 |

|      | 16.5.1  | FADD.D—Double-Precision Floating-Point Add Instruction                                               | 236 |

|      | 16.5.2  | FCLASS.D—Double-Precision Floating-Point Classification Instructions                                 | 237 |